# Boletín Científico del Instituto de Ciencias Básicas e Ingeniería

Publicación Semestral Pädi No. 11 (2018) 81-86

# Compuerta NAND CMOS para Módulo de Electrónica

José Luis González Vidal a,\*, Alejandro Castaño Hernández a, Francisco Morales Jiménez a

<sup>a</sup> Instituto de Ciencias Básicas e Ingeniería - UAEH, Ciudad del Conocimiento, Carretera Pachuca-Tulancingo Km. 4.5, Col. Carboneras, Mineral de la Reforma, Hidalgo, México.

#### Resumen

Los circuitos integrados VLSI (gran escala de integración), son aquellos que se caracterizan por sus dimensiones extremadamente pequeñas, constituidos principalmente por transistores de efecto de campo de metal óxido semiconductor (MOSFET), cuyas longitudes de canal son inferiores al micrómetro, permitiendo integrar un mayor número de transistores en un solo diseño. En el presente trabajo, se diseña una compuerta NAND basada en la tecnología CMOS en la herramienta L-Edit de Tanner Eda, realizando los cálculos matemáticos necesarios para la determinación de las relaciones W, L de los transistores MOSFET, siguiendo las reglas de diseño establecidas al momento del diseño del respectivo layout. Para la creación de bibliotecas de diseño y su posterior utilización en circuitos integrados más grandes y complejos.

Palabras Clave: Circuitos Integrados, VLSI, NAND, MOSFET.

#### 1. Introducción

Los circuitos integrados electrónicos modernos de gran escala de integración (VLSI), utilizan la tecnología CMOS, de la cual, sus características principales son un mayor número de transistores por milímetro cuadrado y disipan menos potencia, siendo éstas piezas claves y fundamentales para un sin número de aplicaciones en aparatos electrónicos digitales. Los circuitos CMOS son circuitos electrónicos analógicos, digitales o mixtos configurados a partir de transistores PMOS y NMOS y sus aplicaciones van desde circuitos integrados de aplicación general o específica, como tarjetas electrónicas para sistemas embebidos, microcontroladores, microprocesadores, aplicaciones en todos los campos donde se requiera un dispositivo o aparato electrónico, tales como relojes, tabletas electrónicas, aparatos de medición, telecomunicaciones videojuegos e internet de la cosas, entre otras (Gray. et al, 2009).

Los transistores MOS tienen un fundamento físico diferente a los BJT (Shockley et al, 1951, Bardeen et al, 1948); los MOS son dispositivos de efecto de campo (Field Effect Transistor, FET) basados en el cambio de comportamiento de la capa de la superficie del semiconductor en una estructura Metal-Óxido-Semiconductor. Aparte de la preliminar patente de Lilienfeld (1934), los primeros trabajos sobre el comportamiento de esta simple estructura son debidos, de nuevo, a W. Shockley (1951), si bien el primer dispositivo transistor MOS fue fabricado en 1960 por Kahng (1960), luego mejorado por el mismo Kahng y Atalla (1976). La tecnología de circuitos integrados tiene su origen en 1959, tras los trabajos de Jack Kilby (1959) de Texas Instruments y Robert Noyce de Fairchild Semiconductors (Noyce, 1959). En agosto de 1959 Fairchild Semiconductors hace pública la tecnología de fabricación de transistores en un proceso planar y, en marzo de 1960 Texas Instruments anuncia el primer circuito integrado comercial, un multivibrador basado en dispositivos semiconductores BJT de silicio (Rubio, 2003).

El propósito del presente trabajo, consiste en mostrar el proceso seguido para el diseño de una compuerta NAND con tecnología CMOS, incluyendo los cálculos matemáticos para la determinación de la relación ancho (W) y largo del canal (L), tanto para el transistor de canal N, como de canal P. Finalizando con la descripción del desarrollo del diseño de la compuerta NAND en la herramienta L-Edit de Tanner Eda, no sin antes realizar la verificación del correcto funcionamiento del circuito al efectuar la pertinente simulación en el software MULTISIM®, modificando los parámetros de los modelos utilizados (Chen, 2006; Gray, 2009; Olandoski, 2016; Razavi, 2001; Villaseñor, 2012; Uyemura, 2002).

A continuación, se describirán las fases de fabricación y el concepto de dibujo de capas (layers) de un circuito CMOS típico (bulk technology), en donde los componentes se construyen sobre un sustrato. Los transistores PMOS deben estar implantados sobre un sustrato tipo n, y los transistores NMOS sobre un sustrato p. Para poder acomodar ambos tipos de transistores sobre un mismo sustrato es preciso crear regiones de suficiente extensión que actúen como sustratos, a estas regiones se les acostumbra a denominar pozos (wells). Dependiendo de las maneras en cómo se crean estas regiones dan lugar a tres tipos de tecnología CMOS.

En la tecnología denominada de pozo N (N-well), el sustrato es de tipo P por lo que se colocan a los transistores NMOS directamente y, es preciso implantar un pozo N para colocar a los transistores PMOS. Una tecnología dual de esta es la tecnología de pozo P (P-well) en donde el sustrato es de tipo N y se implanta una región P. La tercera alternativa consiste en implantar los transistores sobre pozos N y P, especialmente creados (tecnología de pozos gemelos, twin-well). En esta

\* Autor en correspondencia.

tecnología se consigue un mayor y más independiente control de las tensiones umbral de los transistores, tanto PMOS como NMOS, y reduce las caídas de tensión en los sustratos, efecto que puede provocar problemas de latch-up (Gray et al, 2009), (Razavi, 2001).

Relación de máscaras físicas y capas de diseño en una tecnología CMOS twin-well: Estas máscaras se utilizan para la aplicación selectiva de reactivos en las diversas fases del proceso. El número de pasos o subprocesos de fabricación es superior al número de máscaras, según se expondrá más adelante; dichas máscaras, siguiendo un orden de aplicación,

- Máscara de implantación del pozo N (N-well Implant Mask). Define las zonas sobre las que podrán implementarse transistores PMOS.

- Máscara de implantación del pozo P (P-well Implant Mask). Define las zonas sobre las que podrá implementarse transistores NMOS.

- Máscara de área activa (Active Area Mask). Define las zonas sobre las que podrán implantarse transistores. Fuera de esta zona aparecerán capas de óxido grueso.

- Máscara de polisilicio (Polysilicon Mask). Define las regiones sobre las que discurrirán líneas de polisilicio. En las regiones donde el polisilicio intersecciona con área activa, el polisilicio constituye la puerta de un transistor, depositada sobre óxido fi no (óxido de la puerta del MOS).

- Máscara de implantación P+ (P+ Implant Mask). Define las regiones sobre las que se difunde o implanta una región tipo P (drenador y fuente de los transistores PMOS y contactos de polarización del pozo P).

- Máscara de implantación N+ (N+ Implant Mask). Define las regiones sobre las que se difunde o implanta una región tipo N (drenador y fuente de los transistores NMOS y contactos de polarización del pozo N). Esta máscara es complementaria a la máscara anterior.

- Máscara de contactos (Contact Mask). Define el grabado del óxido con las que el primer nivel de metal hace contacto eléctrico con el de polisilicio.

- Máscara de Metal 1 (Metal 1 Mask). Definición de las interconexiones de Metal1.

- Máscara de Vias (Via Mask). Define las perforaciones del óxido a través de las cuales el Metal 1 hace contacto eléctrico con el Metal 2.

- Máscara de Metal 2 (Metal 2 Mask). Define las interconexiones de Metal 2.

- Máscara de pasivación (Passivation Mask). Corresponde a la definición de la capa de óxido de protección final del circuito. Esta capa, típicamente, cubre todo el circuito a excepción de los puntos de conexión final con las terminales del encapsulado.

El diseño microelectrónico corresponde a la definición de estas máscaras. Ello se hace mediante el dibujo de rectángulos (geometría Manhattan) que constituyen las capas del diseño y a partir de las cuales se pueden crear las máscaras físicas. En el diseño VLSI de circuitos en la tecnología anterior, estas capas podrían ser 9: Pasivación, Metal 2, Vía, Metal 1, Contactos,

Implantación P+ (la Implantación N+ es complementaria), Polisilicio, Área activa y Pozo N (el pozo P es complementario). Una característica de una tecnología es la resolución mínima de un dibujo de capas (layout). Esta dimensión, usualmente indicada como λ, tiene fuerte repercusión en las características eléctricas.

#### 2. Desarrollo

#### Ecuaciones de los transistores MOSFET en la región de saturación.

Para determinar la relación W y L, es decir, el largo y ancho de canal, se emplearon las siguientes ecuaciones, las cuales corresponden a la corriente entre el drenador y la fuente en su modalidad de saturación IDS, debido a que se desea que los transistores NMOS y PMOS conduzcan.

Transistor MOSFET de canal n:

$$I_{DS} = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_T)^2 (1 + \lambda V_{DS})$$

(1)

Transistor MOSFET de canal p:

$$I_{SD} = \frac{1}{2} \mu_P C_{ox} \frac{W}{L} (V_{SG} - |V_T|)^2 (1 + \lambda V_{SD})$$

(2)

$I_{DS}$ : Corriente entre el drenador y la fuente.

$\mu_n$ : Movilidad superficial de los portadores.

$C_{ox}$ : Capacitancia del óxido de la compuerta.

W: Ancho del canal.

L: Largo del canal.

$V_{GS}$ : Voltaje entre la compuerta y la fuente.

$V_T$ : Voltaje de Umbral.

$V_{DS}$ : Voltaje entre el drenador y la fuente.

Como puede notarse en (1) y (2), es necesario conocer el voltaje de umbral del transistor con el que se esté trabajando,

por lo cual se utilizarán las siguientes ecuaciones para determinar dicho valor para el NMOS y PMOS a diseñar.

$$V_{t} = 2\phi_{b} + \frac{\sqrt{2\varepsilon_{si}qN_{A}*2\phi_{b}}}{c_{ox}} + V_{fb}$$

$$\phi_{b} = \frac{kT}{q}ln\left(\frac{N_{A}}{n_{i}}\right)$$

$$C_{ox} = \frac{\varepsilon_{ox}}{t_{ox}}$$

$$\beta_{n} = K_{n}\left(\frac{W}{L}\right) = \frac{\mu_{n}\varepsilon_{ox}}{t_{ox}}\left(\frac{W}{L}\right)$$

$$\beta_{p} = K_{p}\left(\frac{W}{L}\right) = \frac{\mu_{p}\varepsilon_{ox}}{t_{ox}}\left(\frac{W}{L}\right)$$

$$(5)$$

$$\beta_{p} = K_{p}\left(\frac{W}{L}\right) = \frac{\mu_{p}\varepsilon_{ox}}{t_{ox}}\left(\frac{W}{L}\right)$$

$$(7)$$

$$\emptyset_b = \frac{kT}{a} \ln \left( \frac{N_A}{n_i} \right) \tag{4}$$

$$C_{ox} = \frac{\varepsilon_{ox}}{t_{ox}} \tag{5}$$

$$\beta_n = K_n \left( \frac{w}{I} \right) = \frac{\mu_n \varepsilon_{ox}}{I} \left( \frac{w}{I} \right) \tag{6}$$

$$\beta_p = K_P \left( \frac{W}{L} \right) = \frac{\mu_p \varepsilon_{ox}}{t_{ox}} \left( \frac{W}{L} \right) \tag{7}$$

Dónde:

$K_n$ : Ganancia del semiconductor n

$K_P$ : Ganancia del semiconductor p

$N_A$ : Densidad de los aceptores.

$V_{fb}$ : Voltaje de banda plana.

$V_t$ : Voltaje de Umbral.

n<sub>i</sub>: Concentración intrínseca del silicio

$(1.45X10^{10}cm^{-3} \ a\ 300K)$

$t_{ox}$ : Espesor del aislante de la compuerta.

$\beta_n$ : Constante beta para el transistor NMOS.

$\beta_p$ : Constante beta para el transistor PMOS.

$\varepsilon_{ox}$ : Permitividad del dioxido de silicio.

$(3.4515 * 10^{-13} F/cm)$

$\varepsilon_{si}$ : Permitividad del silicio. (1.06 \*  $10^{-12} F/cm$ ).  $\mu_P$ : Movilidad superficial de los portadores mayoritarios (huecos 180cm²/V.seg).  $\mu_n$ : Movilidad superficial de los portadores mayoritarios (electrones 500cm²/V.seg). T: Temperatura en grados kelvin.  $k: Constante\ de\ Boltzman\ (1.38*10^{-23} J/K)$ q: Carga del electrón  $(1.6 * 10^{-19}C)$

#### Cálculo del ancho de canal Wn del transistor NMOS

Considerando que  $N_A = N_D = 10^{16} \text{ cm}^{-3} \text{ y los siguientes}$ valores se calcula W<sub>n</sub>:

Primero se calcula  $\emptyset_{bn}$ :

$$\begin{split} \phi_{bn} &= \frac{kT}{q} ln \left( \frac{N_D}{n_i} \right) \\ &= \frac{(1.38 * 10^{-23} J/K)(300°K)}{(1.6 * 10^{-19} C)} ln \left( \frac{10^{16} cm^{-3}}{1.45 * 10^{10} cm^{-3}} \right) \\ &= 0.347862 \, V \\ \phi_{bn} &\approx 0.35 \, V \end{split}$$

Se calcula la capacitancia del óxido de la compuerta considerando los siguientes valores

$$C_{ox} = \frac{\varepsilon_{ox}}{t_{ox}} = \frac{t_{ox} = 20 * 10^{-9} cm}{3.4515 * 10^{-13} F/cm} = 17.2575 \mu F$$

Ahora se obtiene el voltaje de umbral una vez calculado los valores necesarios, se propone  $V_{fb} = -0.9V$  para el transistor **NMOS**

$$V_{tn} = 2\phi_b + \frac{\sqrt{2\varepsilon_{si}qN_A * 2\phi_b}}{C_{or}} + V_{fb}$$

$$\begin{split} V_{tn} &= 2(0.35V) \\ &+ \frac{\sqrt{2(1.06*10^{-12}F/cm)(1.6*10^{-19}C)(10^{16}cm^{-3})*2(0.35V)}}{17.2575\mu F} - 0.2V \\ &V_{tn} &= 0.5028235733V \approx 0.5V \end{split}$$

considerando los siguientes valores para el transistor NMOS, tenemos:

$$V_S = 3.5 \ V, V_t = 0.5 V, V_D = 1 V, V_G = 5 V \ K_P = \ \ ? \ W_n = \ \ ? \ L_n = 0.9 \ \mu m, I_{DS} = 4.8 mA$$

Donde

$$K_n = \frac{\left(500 \frac{cm^2}{v \ seg}\right) (3.9) \left(8.85 * \frac{10^{-14} F}{cm}\right)}{20 * 10^{-9} cm}$$

$$= \frac{8.62875 mA}{V^2} \approx 8.63 * 10^{-3} A/V^2$$

Despejando a  $W_n$  se tiene:

$$W_n = \frac{2I_{DS}L_n}{K_n(V_{GS} - V_t)^2} = \frac{2(4.8mA)(0.9\mu m)}{(8.63 * 10^{-3}A/V^2)(1.5V - 0.5)^2}$$

$$= 1.001158749\mu m \approx 1\mu m$$

# Cálculo del ancho de canal Wp del transistor PMOS

Para el diseño de un transistor PMOS, se considerará una densidad de portadores  $N_A = 10^{16} \text{ cm}^{-3}$ . Primero se calcula  $\emptyset_{bp}$ :

$$\begin{split} \emptyset_{bp} &= \frac{kT}{q} ln \left( \frac{N_A}{n_i} \right) \\ &= \frac{(1.38 * 10^{-23} J/K)(300°K)}{(1.6 * 10^{-19} C)} ln \left( \frac{10^{16} cm^{-3}}{1.45 * 10^{10} cm^{-3}} \right) \\ &= 0.347862 \, V \end{split}$$

Ahora se obtiene el voltaje de umbral una vez calculado los valores necesarios, se propone  $V_{fb} = -0.2V$  para el transistor

$$\begin{split} V_{tp} &= 2\emptyset_b + \frac{\sqrt{2\varepsilon_{si}qN_A * 2\emptyset_b}}{C_{ox}} + V_{fb} \\ V_{tp} &= 2(0.35V) \\ &+ \frac{\sqrt{2(1.06*10^{-12}F/cm)(1.6*10^{-19}C)(10^{16}cm^{-3})*2(0.35V)}}{17.2575\mu F} \\ &- 0.9V \\ V_{tp} &= -0.1971760171V \approx -0.2V \end{split}$$

Considerando los siguientes valores para el transistor PMOS, tenemos:

$$\begin{split} V_S = 5V \; V_t = -0.2V \; V_D = 1V \; V_G = 3.5V \; K_P =_{\dot{\xi}}? \; W_P =_{\dot{\xi}}? \\ L_P = 1.1 \; \mu m \; I_{DS} = 4.8 mA \end{split}$$

$$K_{P} = \frac{\left(180 \frac{cm^{2}}{v \, seg}\right) (3.9) \left(8.85 * \frac{10^{-14}F}{cm}\right)}{\frac{20 * 10^{-9}cm}{L_{P}}} W_{p}$$

$$= \frac{\frac{3.10635mA}{V^{2}} W}{L_{P}} \approx 3.11 * 10^{-3} A/V^{2}$$

Despejando a

$$W_p$$

se tiene:

$$W_p = \frac{2I_{DS}L_P}{K_P(V_{SG} - |V_t|)^2} = \frac{2(4.8mA)(1.1\mu m)}{(3.11*10^{-3}A/V^2)(1.5V - 0.2V)^2}$$

$$W_p = 2.009170646\mu m \approx 2\mu m$$

#### 3. Resultados

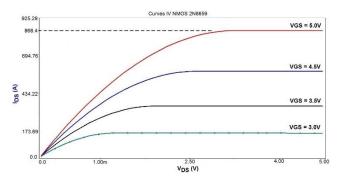

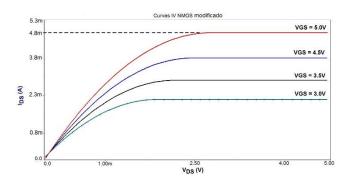

Para el caso del transistor tipo n, se efectuaron las modificaciones pertinentes de las características del transistor NMOS (2N6659) en el simulador MULTISIM®. En las figuras 1 y 2, se muestras las curvas del análisis corriente voltaje (IV) obtenidas al simular tanto el transistor NMOS original como para el modificado. En la figura 1 se observa que para Vds = Vgs = 5V, se obtiene una  $I_{DS} = 868.4 \text{mA}$ ; por otra parte, para el transistor diseñado, se obtuvo una  $I_{DS}$ = 4.8mA para  $V_{DS}$  =  $V_{GS}$ = 5V (Figura 2).

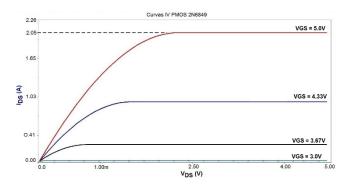

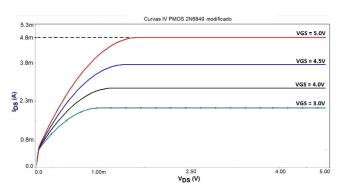

Para el caso del transistor tipo p, se efectuaron las modificaciones pertinentes de las características del transistor PMOS (2N6849) en el simulador MULTISIM®. En las figuras 3 y 4, se muestra la simulación del análisis IV tanto para el transistor PMOS original, así como para el modificado; En la figura 3 se observa que para  $V_{DS} = V_{GS} = 5V$ , se obtiene una I<sub>DS</sub>= 2.05mA; mientras que, en la figura 4, se observa la gráfica

Figura. 1. Curvas obtenidas con el Analizador IV de la corriente en el transistor NMOS original (2N6659).  $I_{DS}$ = 868.4mA,  $V_{DS}$  =  $V_{GS}$  = 5V

Figura. 2. Curvas obtenidas con el Analizador IV de la corriente en el transistor NMOS modificado.

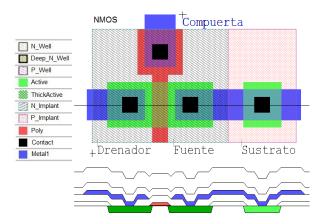

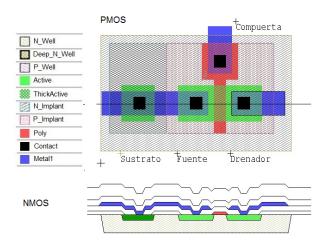

del transistor PMOS modificado, donde se obtuvo una  $I_{DS}$ = 4.8mA para  $V_{DS} = V_{GS} = 5V$ . Siguiendo las reglas de diseño para circuitos integrados, se construyeron los layouts de los transistores NMOS y PMOS con el software L-EDIT de TANNER EDA, obteniendo los resultados mostrados en las figuras 5 y 6, incluyendo además el respectivo corte seccional que permite visualizar los diferentes materiales utilizados, es decir las capas del layout.

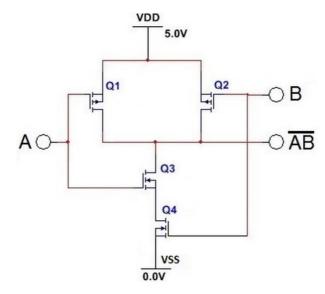

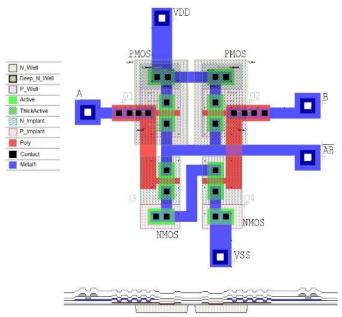

Una vez diseñados los transistores NMOS y PMOS, se diseña una compuerta NAND (figura 7), el circuito digital que fue previamente simulado en la herramienta MULTISIM®; el diseño se basa en colocar dos transistores PMOS Q1 y Q2 en paralelo, los transistores NMOS Q3 y Q4 se conectan en serie. La entrada de alimentación VDD está conectada a las fuentes de Q1 y Q2, la entrada A se conecta a las compuertas de Q1 y Q3, la entrada B se conecta a las compuertas de Q2 y Q4, la salida  $\overline{AB}$  está conectada a los drenadores de Q1, Q2 y Q3. y, la entrada de alimentación VSS está conectada a la fuente de Q4.

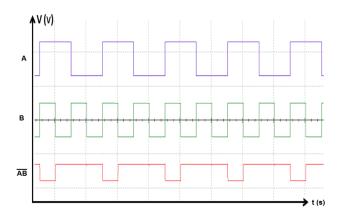

En la figura 8, se muestra la simulación de la compuerta NAND de dos entradas implementada con tecnología CMOS; como se puede apreciar, cuando las entradas A o B tienen un nivel alto (5V) se obtiene un nivel bajo (0V) a la salida  $\overline{AB}$ , debido a que Q1 y Q2 se encuentran en corte y están en paralelo, mientras que los NMOS se encuentran en saturación y están conectados en serie, de esta forma el valor de la tensión VSS se transfiere a la salida  $\overline{AB}$ . Por otra parte, un nivel bajo (0V) en cualquiera de las entradas A o B se obtiene un nivel alto (5V) a la salida  $\overline{AB}$ .

debido a que Q1 y Q2 se encuentran en saturación, mientras que los NMOS se encuentran en corte, de esta forma el valor del

Figura. 3. Curvas obtenidas con el Analizador IV de la corriente en el transistor PMOS, Original (2N6849). Id= 2.05A, Vds = Vgs = 5V

Figura. 4. Curvas obtenidas con el Analizador IV de la corriente en el transistor PMOS modificado.

Figura. 5. Diseño layout del transistor NMOS con L-EDIT de TANNER EDA.

Figura. 6. Diseño layout del transistor PMOS con L-EDIT de TANNER EDA.

voltaje de alimentación VDD se transfiere a la salida AB. En la figura 9, se muestra el diseño final del layout de la compuerta NAND, cuya elaboración se siguió en base a las respectivas reglas de diseño; ocupando un área de 63.5μm x 76.4μm, así como a las consideraciones de las relaciones de W, L tanto para el transistor NMOS, como PMOS, cuyos valores fueron previamente calculados en las secciones anteriores; como se puede observar, los dos transistores PMOS se conectan en paralelo, mientras que los transistores NMOS en serie, compartiendo drenador y fuente en una de las respectivas conexiones, lo que permite lograr la conexión antes mencionada. Por cuestiones de espacio, para los contactos a región activa se utilizaron dos contactos en las fuentes de todos los transistores y, se utilizaron cuatro contactos a polisilicio (compuerta) con el metal de las entradas A y B, con la ayuda del corte seccional, se visualizan claramente los contactos a polisilicio y los materiales utilizados de la compuerta NAND diseñada.

## 4. Discusión

Los sistemas VLSI tienen la principal característica que permiten una gran cantidad de dispositivos por unidad de área, esto conlleva a que se pueden integrar circuitos electrónicos con muchos transistores, ocupan menos espacio físico, pero con un consumo mínimo de potencia, además de que su producción en

Figura 7. Compuerta NAND simulada en la herramienta MULTISIM.

Figura 8. Visualización de las señales de entrada (señal azul y verde) de la compuerta NAND, así como la respectiva salida (señal roja).

caso de la compuerta lógica NAND diseñada, ésta fue seleccionada debido a que es la compuerta la más versátil de todas, ya que, con la compuerta NAND se pueden implementar todas las demás compuertas lógicas, la compuerta diseñada cumple con las reglas de diseño, además de que se calcularon principales valores de los transistores NMOS y PMOS utilizados, como voltaje de umbral  $W_n$ ,  $L_n$ ,  $W_p$  y  $L_p$  y se obtuvieron corrientes de 4.8mA para ambos transistores, contra 868.4mA y 2.05A de los NMOS y PMOS originales respectivamente, lo cual indica un ahorro de potencia muy sustancial. El diseño completo de la nueva compuerta NAND ocupa un área mínima de 63.5μm x 76.4μm, misma que se podrá utilizar en nuevas aplicaciones importantes tales como las tradicionales compuertas lógicas, flip flops, latches, codificadores, decodificadores, registros de corrimiento y hasta microprocesadores y microcontroladores.

#### 5. Conclusiones

Los circuitos integrados utilizan principalmente los transistores NMOS y PMOS (tecnología CMOS), con los cuales se pueden generar un sin número de aplicaciones, tanto analógicas como digitales, tal como ya se ha mencionado. En el presente trabajo, se lograron diseñar un transistor NMOS y otro PMOS, en base

Fig. 9. Layout de una compuerta NAND con la herramienta L-EDIT de Tanner EDA. Corte seccional.

a una corriente propuesta I<sub>D</sub>=4.8mA, para lo cual fue necesario, realizar cálculos matemáticos para la determinación del potencial del bulk  $\emptyset_b$ , voltaje de umbral  $V_t$  y posteriormente las relaciones  $W_P \approx 2\mu m$ ,  $L_P = 1.1\mu m$ ,  $W_n \approx 1\mu m$ , y  $L_P = 0.9\mu m$ , considerando además un sin número de datos importantes para ello y, ocupando un área mínima de 63.5μm x 76.4μm. Se comprobó el funcionamiento de los transistores NMOS, PMOS y la compuerta NAND, por medio de las simulaciones con el programa Multisim®, para la corriente de I<sub>D</sub>=4.8mA. Se describieron las máscaras más importantes que se utilizaron en este diseño y, además, se realizaron los diseños de los transistores NMOS, PMOS y la compuerta NAND en L-EDIT®. Con lo anterior, se adquirió un conocimiento importante en el diseño de circuitos integrados de gran escala de integración, la cual será el primer diseño para crear una biblioteca propia de dispositivos para múltiples aplicaciones.

## **English Summary**

# Design of Large Scale Circuits: NAND Gate CMOS Abstract

VLSI integrated circuits (large scale integration) are those that are characterized by their extremely small dimensions, consisting mainly of semiconductor oxide metal field effect transistors (MOSFET), whose channel lengths are less than micrometer, allowing the integration of a greater number of transistors per cm² in a single design. In the present work, a NAND gate based on CMOS technology is designed by Tanner Eda's L-Edit tool, performing the necessary mathematical calculations for the determination of the W, L ratios of the MOSFET transistors, following the established design rules at the time of designing the respective layout. For the creation of design libraries and their subsequent use in larger and more complex integrated circuits.

#### Keywords:

Integrated circuits VLSI, NAND gate, MOSFET.

#### Agradecimientos

Este trabajo ha sido realizado gracias al apoyo de la Universidad Autónoma del Estado de Hidalgo.

#### Referencias

Antonio Rubio et al, (2003), Diseño de circuitos y sistemas integrados, Edicions UPC, pp 37, ISBN: 84-8301-564-1

Bardeen, J., and Brattain, W. H., (1948) "The Transistor, A Semi-Conductor Triode", Phys. Rev. 74, pp. 130-231.

Chen, Wai-Kai, (2006), The VLSI Handbook, CRC Press, 2nd ed,

Gray P. R. et al, (2009), Analysis and Design of Analog Integrated Circuits, 5a Ed, Ed Wiley.

Khang, D. and Atalla, M. M., (1960), "Silicon-Silicon Dioxide Field Induced Surface Devices", IRE Solid-State Device Res. Conf., Carnegie Institute of Technology, Pittsburgh, Pa.

Khang, D., (1976), "A Historical Perspective on the Development of MOS Transistors and Related Devices", IEEE Trans. Electron Devices, ED-23, 655.

Kilby, J. S. (1964), "Miniaturized Electronic Circuits", U.S. Patent 3,138,743, (filed February 6, 1959)

Lilienfeld J. E., (1933), Device for controlling electric current, US1900018 (A) — 1933-03-07.

Noyce, R. N. (1959), "Semiconductor Device-and-Lead Structure", U.S. Patent 2,918,877, April 25 led July 30, 1959).

Razavi, B., (2001), Desing of Analog CMOS Integrated Circuits, Mc Graw-Hill.

Shockley, W. and Pearson, G. L., (1948), "Modulation of Conductance of Thin Films of Semi-Conductors by Surface Charges", Phys. Rev., pp. 232-233

Shockley, W., Sparks, M. and Teal, G. K., (1951), "p-n Junction Transistors", Phys. Rev. 83, pp. 151-162.

Uyemura, J. P., (2002), Introduction to VLSI Circuits and Systems, Ed Wiley and Sons.

Villaseñor, J. R. y Hernández F. A., (2012), Circuitos Eléctricos y Aplicaciones Digitales - 2ª Edición, Pearson Educación; 2ª Edición. Olandoski, M., (2016), Diseño Lógico de Circuitos de Conmutación -

Vol.2: Circuitos Secuenciales. Ed. Marcos Olandoski. Bifurcación: